Abstract

Free full text

Defects Contributing to Hysteresis in Few-Layer and Thin-Film MoS2 Memristive Devices

Abstract

Molybdenum disulfide, a two-dimensional material extensively explored for potential applications in non-von Neumann computing technologies, has garnered significant attention owing to the observed hysteresis phenomena in MoS2 FETs. The dominant sources of hysteresis reported include charge trapping at the channel–dielectric interface and the adsorption/desorption of molecules. However, in MoS2 FETs with different channel thicknesses, the specific nature and density of defects contributing to hysteresis remain an intriguing aspect requiring further investigation. This study delves into memristive devices with back-gate modulated channel layers based on CVD-deposited flake-based and thin-film-based MoS2 FETs, with a few-layer (FL) and thin-film (TF) channel thickness. Analysis of current–voltage (

1. Introduction

For advanced technology nodes, molybdenum disulfide (MoS2), a widely studied two-dimensional (2D) material, has raised the expectations to accommodate further scaling of the channel length, mitigate short-channel effects, and enhance electrostatic gate control beyond what is achievable for Si-based devices. MoS2 as a channel layer in field-effect transistors (FETs) has demonstrated remarkable performance metrics, including high mobility (

Recent years have witnessed a growing interest in FETs based on MoS2 nanosheets due to the hysteresis phenomena observed in their conductance, presenting opportunities to be utilized in non-von Neumann computing technologies [5,9,10,12,19,20]. However, understanding the nature of hysteresis in MoS2 FETs is complex and diverse, in particular due to the variations across devices and cycles [10,12,19,21]. Determining and distinguishing the factors contributing to hysteresis and comprehending their associated behavior in the operations of MoS2 FETs is still under investigation due to the complex interplay of multiple mechanisms [21]. Developing a comprehensive understanding of the underlying factors is therefore crucial to accurately determine and control their influence over hysteresis [21]. The origin of hysteresis in MoS2 FETs has been studied by several research groups, mostly reported as arising from various intrinsic and extrinsic factors [7,16,17,22]. Primarily, charge trapping at the channel–dielectric interface or adsorption/desorption of H2O or O2 molecules have been identified as the dominant sources of hysteresis [3,16,20,21,23]. However, in MoS2 FETs with different channel thicknesses, the nature and density of defects contributing to hysteresis remain a question of interest requiring further investigation.

This study involves experimental investigations on the hysteresis behavior of flake-based and thin-film-based back-gate MoS2 FETs on a SiO2/Si substrate with a few-layer (FL) and thin-film (TF) channel thickness, respectively. The findings revealed that both the FL and TF MoS2 FETs exhibited a clockwise hysteresis behavior dominated by intrinsic and interface defects within the device channel. Notably, the TF MoS2 FET exhibited increased hysteresis compared to the FL FET, particularly with a higher gate voltage and sweeping range. The increased hysteresis in the TF MoS2 FET cannot be attributed solely to defects near the channel–dielectric interface, indicating a significant contribution from increased intrinsic defect density within the channel as the thickness increases.

2. Materials and Methods

2.1. Material Characterization

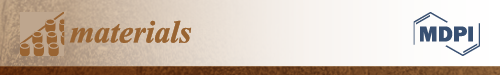

MoS2 flakes and thin films were deposited through chemical vapor deposition (CVD) on a heavily doped p+Si substrate (orientation <100> ±0.50°, resistivity 1–5

SEM images of CVD-deposited (a) individual MoS2 flakes and (b) a uniformly deposited thin film on a SiO2/Si substrate, which were employed in the fabrication of back-gate FETs.

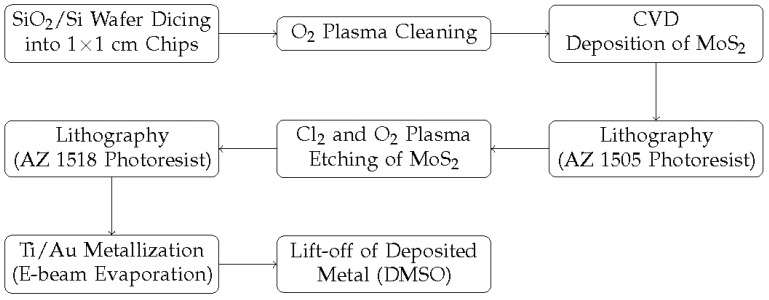

The CVD-deposited MoS2 flakes and thin films were subsequently characterized by Raman spectroscopy (Witec Alpha 300R, excitation wavelength of 488 nm) at room temperature. Afterward, the MoS2 flakes and thin-film samples were cleaned, pre-baked, coated with an adhesion promoter (HMDS), and then spin-coated at 4000 rpm with a positive resist (AZ 1505). Following this, the MoS2 channel was defined by patterning the resist through image inversion using a maskless lithography machine (MLA 150 Heidelberg Instruments). Exposed patterns were then developed in a developer solution (AZ 351-B) for 30 s. Subsequent to this step, the samples underwent etching using CL2 and O2 plasma for 1 min, and the resist was removed using acetone afterward. To fabricate contact leads for the back-gate FETs, both samples underwent a coating of HMDS and were subsequently spin-coated with another positive resist (AZ 1518) at 4000 rpm. The metal contacts were then defined by patterning the resist using image inversion with the maskless lithography machine. Exposed patterns were developed in a developer solution (AZ 351-B) for 30 s. Following development, the samples were metalized through electron beam evaporation to deposit the Ti (10 nm)/Au (80 nm) films. The standard lift-off process was employed later to remove the metal residuals in DMSO for 30 min, completing the contact fabrication for the back-gate MoS2 FETs. A simplified schematic outlining the fabrication process steps for the MoS2 FETs is illustrated in Figure 2. The FETs derived from individual flakes had a channel length (L) =

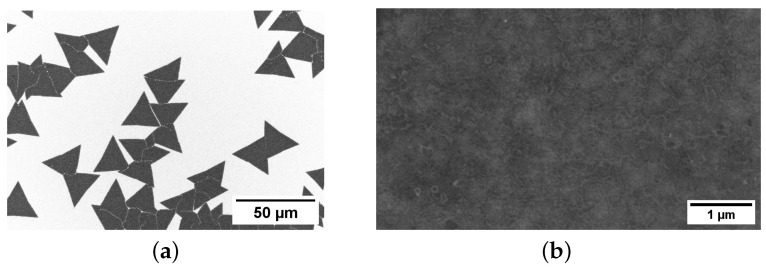

Raman spectra of MoS2 channel obtained from (a,c) flake-based few-layer (FL) and (b,d) thin-film-based (TF) FETs. Three distinct positions on the device channel were measured and highlighted in specific colors, illustrating unique vibrational modes of MoS2, including

The Raman spectra obtained from the channel layer of the experimental back-gate FETs based on a MoS2 flake and thin film are presented in Figure 3a,b, revealing two pronounced first-order Raman active modes of MoS2:

Furthermore, the shear modes (SMs) and layer-breathing modes (LBMs) identified in the low-frequency region (<50 cm−1) of the Raman spectrum were scrutinized and are illustrated in the insets of Figure 3a,b on a logarithmic scale. Analyzing the low-frequency SMs and LBMs allowed for a comprehensive characterization of mono-, few-layered, and thin-film MoS2, complementing the high-frequency Raman measurements, as these Raman active modes also exhibit positional shifts with the layer numbers [28]. Significantly, SMs and LBMs are absent in mono-layers but display a characteristic blue (stiffening) and red (softening) shift, respectively, with the increasing number of layers from 2L to 5L [28]. However, the peak intensity and shift declines as the film thickness progresses from 5L to the bulk [28]. The low-frequency Raman peak positions of the MoS2 flake, presented in the inset in Figure 3a, demonstrated a close agreement with high-frequency measurements and indicated variations in thickness from monolayer to few layers. In positions 1 and 3, there were no explicit SMs and LBMs; however, they were evident in position 2. Conversely, the peak positions of MoS2 thin film, shown in the Figure 3b inset, indicated thin-film characteristics with minor variations in SM and LBM positions and peak intensities.

Subsequently, the surface topography of the MoS2 FET channels was characterized using atomic force microscopy (AFM) measurements, revealing a thickness of approximately a few layers (FL) (~2.8 nm, ~4 monolayers) for the flake-based MoS2 FET and thin film (TF) characteristics (~34 nm) for the thin-film-based MoS2 FET.

2.2. Electrical Characterization

The electrical characterization of the FL and TF MoS2 FETs was conducted in a shielded probe station connected to a Keithley-4200 semiconductor characterization system at room temperature, under a N2 atmosphere, and in darkness, unless stated otherwise. Measurements were conducted in a two-probe configuration, with the FET contact leads serving as the source and drain, while the heavily doped p+Si substrate acted as the global back-gate electrode. Quantitative comparison between devices with varying dimensions (L and W) was performed by normalizing the measured current (

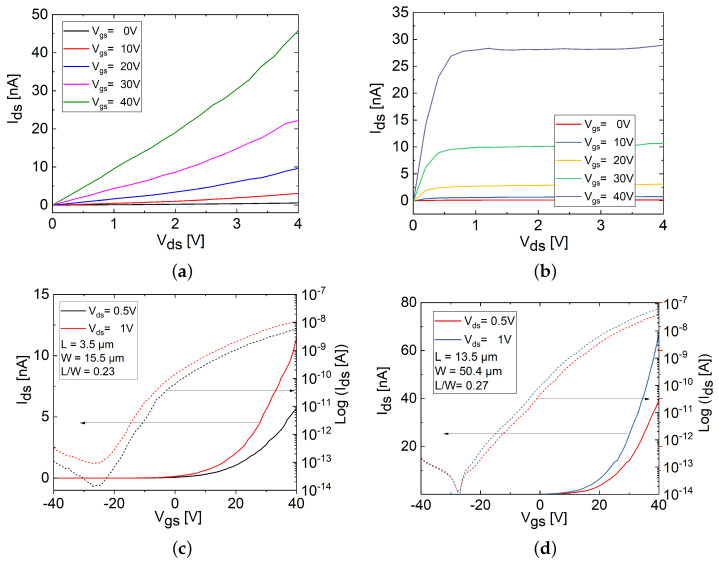

The output (

(a,b) Output (

Figure 4c,d display the transfer (

Table 1

Performance parameters for FL and TF FETs at

| Parameter | Units | FL-FET | TF-FET |

|---|---|---|---|

| nA | ~6 | ~40 | |

| fA | ~18 | ~15 | |

|

| - | ~ | ~ |

| V | 12 | 22 | |

|

| cm2/Vs | 0.02 | 0.17 |

The differing performance between the FL and TF MoS2 FETs can be ascribed to various factors. The nearly Ohmic contact properties observed in the output characteristics of the FL FET, as opposed to the TF FET that demonstrated Ohmic contact properties, signify the presence of a higher SBH and contact resistance (

In contrast, the Ohmic contact properties, lower

Nevertheless, increasing the number of layers in the TF MoS2 structure also gave rise to an increase in the intrinsic defect density, originating from structural inhomogeneity, vacancies, dislocations, or grain boundaries within the channel material [13,15,18]. This increase, in turn, resulted in a higher

3. Results and Discussion

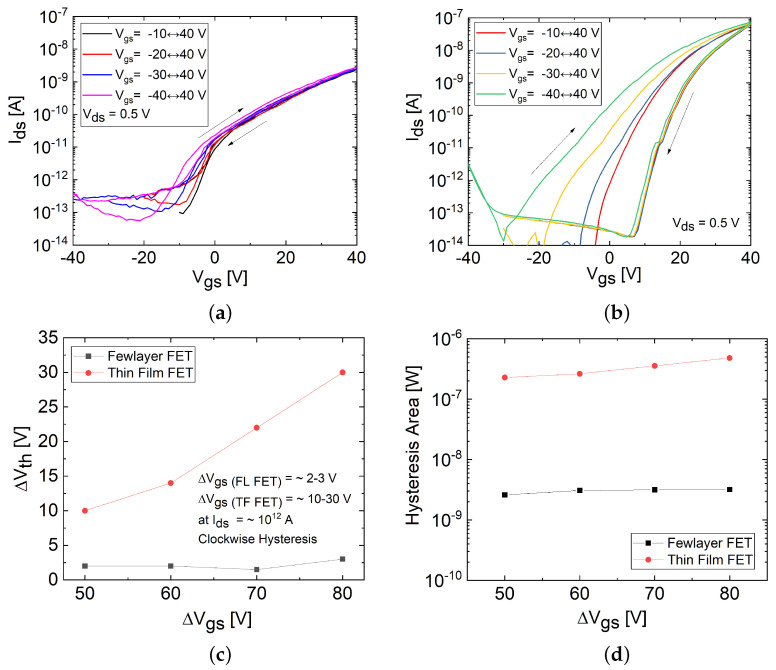

Fluctuations in the number of charge carriers observed during forward (off state to on state) and backward (on state to off state) voltage sweeps in the FL and TF MoS2 FETs, shown in Figure 5a,b, indicate the presence of trap states capturing and releasing charges [3,21]. Trap states originating from several intrinsic and extrinsic factors can affect the charge carrier density, channel current, and lead to

Double-sweep transfer characteristics of (a) FL and (b) TF MoS2 FETs with a decreasing negative start cycle at

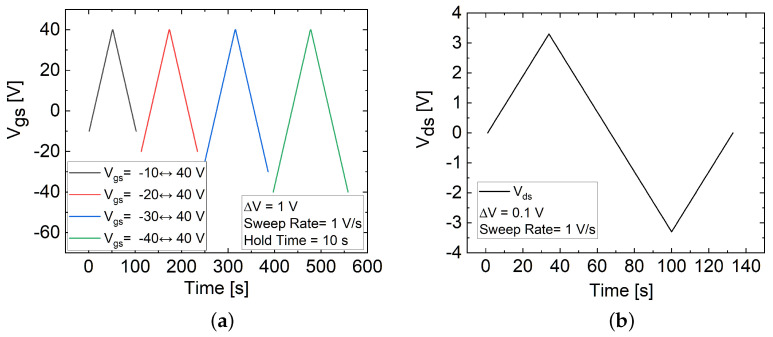

In this study, the underlying causes of hysteresis were investigated by measuring the hysteresis dependence on varying forward and backward

Illustration of double-sweep curves for the MoS2 FETs: (a)

Figure 5a,b present the double-sweep transfer characteristics of the FL and TF FETs, measured in a decreasing negative start cycle, with

Studies conducted on explaining the occurrence of clockwise hysteresis and the asymmetry in

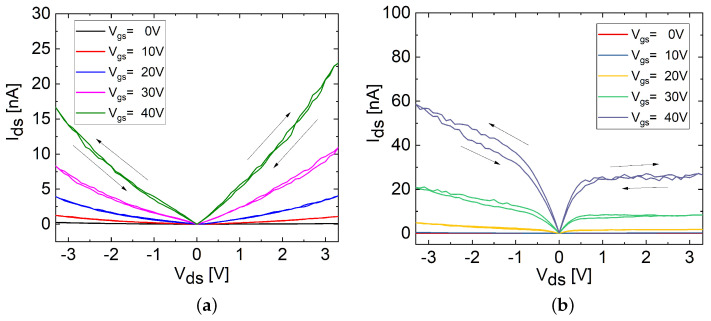

Afterward, the hysteresis characteristics of both the FL and TF FETs were investigated in the double-sweep output curves. As illustrated in Figure 6b, the

Double-sweep output characteristics of (a) FL and (b) TF MoS2 FETs with increasing

The clockwise hysteresis in both device types at room temperature suggests that the underlying sources of hysteresis are similar, and negates the idea that hysteresis was caused by the presence of ions (Na+ and K+) in the SiO2 layer or by oxide traps near the p+Si gate. Because the former factor would lead to counterclockwise hysteresis, and the latter does not exhibit hysteresis at room temperature [21,32]. However, reported studies indicate that in addition to intrinsic or interface defects of MoS2, the adsorption of O2 or H2O molecules on the MoS2 channel surface or at the MoS2/SiO2 interface could also contribute to clockwise hysteresis in an ambient environment [3,20,21,32]. Nevertheless, the results obtained in our study do not support the perception that adsorbate-mediated hysteresis played a dominant role in the observed clockwise hysteresis. This is because our experimental setup was meticulously designed to mitigate changes in humidity. The introduction of N2 purging into the probe station housing played a crucial role in maintaining a controlled environment during the electrical characterization of the FL and TF MoS2 FETs. Prior to introducing the device under test (DUT) into the shielded probe station, the measurement chamber underwent extensive N2 purging for several hours. Additionally, as a precautionary measure, before conducting measurements, the devices were kept inside the chamber for several hours to minimize the potential moisture accumulation on the top surface. The DUT was enclosed within the closed measurement chamber throughout the measurement process, minimizing the influence of gas adsorption [32].

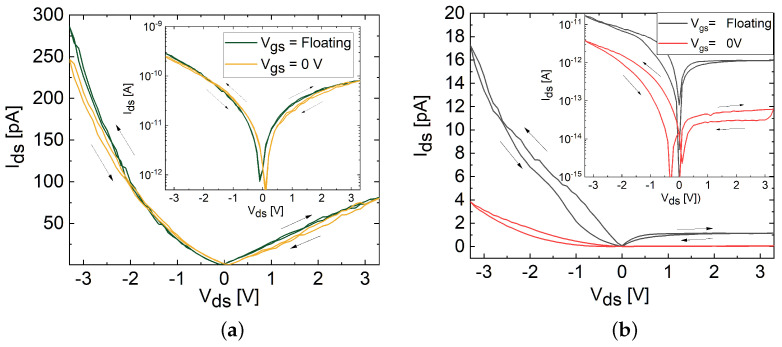

Subsequently, an output measurement analysis involving both floating and grounded (

Double-sweep output characteristics of (a) FL and (b) TF MoS2 FETs at floating and grounded (

This disparity in hysteresis under the floating and grounded gate conditions suggests that under the floating-gate configuration, charge carriers likely traversed through the bulk of the channel, taking advantage of the path with a lower defect density and lower resistance, rather than primarily passing near the interface [18]. Consequently, the channel current was higher where the observed hysteresis can be attributed to the presence of intrinsic defects within the MoS2 channel volume, which tends to increase with layer thickness [18]. This observation aligns with the higher

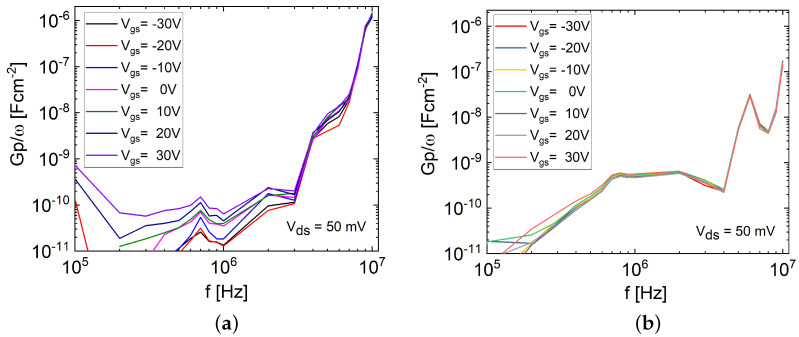

To quantitatively evaluate the density of the interface and intrinsic bulk trap states in the FETs and assess their impact on device performance, conductance–frequency (

Conductance–frequency (

Based on the measured parallel

Here,

Here,

Table 2

Comparison of parameters between FL and TF MoS2 FETs.

| Parameters | FL MoS2 FET | TF MoS2 FET |

|---|---|---|

|

|

| |

|

|

| |

| ~ | ~ |

FET parameters, including the density of states inside the MoS2 channel (

4. Conclusions

In conclusion, the experimental investigations on both the FL and TF MoS2 FETs revealed gate-modulated clockwise hysteresis behavior and an asymmetry in the

Further investigation of double-sweep output characteristics under both floating and grounded gate configurations inferred that under floating-gate conditions, hysteresis was predominantly influenced by the intrinsic defects within the bulk of the channel, leading to higher hysteresis in the TF FETs due to increased defect density with layer thickness. Conversely, under grounded-gate conditions, interface defects played a more significant role, resulting in decreased channel current (

The conductance–frequency (

Acknowledgments

The authors would like to thank Joachim Döll, Manuela Breiter, David Venier, and Jonas Schneegaß from the Center of Micro- and Nanotechnologies (ZMN) (DFG RIsources reference: RI_00009), a DFG-funded core facility (Grant No. MU 3171/2–1 + 6–1, SCHA 632/19–1 + 27–1, HO 2284/4–1 + 12–1) at TU Ilmenau, for their support with the experiments concerning the fabrication of devices.

Funding Statement

The financial support of this research was provided by the Carl Zeiss Foundation under Contract P2018-01-002. The work was supported in addition by the European Fund for Regional Development (EFRE-OP 2014–2020 and FKZ Raman 2021 FGI 0032) as part of the REACT-EU program as a reaction to the COVID-19 pandemic.

Author Contributions

Conceptualization, S.A., V.K. and J.P.; methodology, S.A., V.K., S.M. and S.T.; software, S.A.; validation, S.A., V.K., S.M. and J.P.; formal analysis, S.A., V.K. and S.M.; investigation, S.A.; resources, S.A., V.K., S.M. and S.T.; data curation, S.A., V.K., S.M. and S.T.; writing—original draft preparation, S.A.; writing—review and editing, S.A., V.K. and J.P.; visualization, S.A.; supervision, V.K., J.P. and H.O.J.; project administration, J.P. and H.O.J.; funding acquisition, J.P. All authors have read and agreed to the published version of the manuscript.

Data Availability Statement

The data presented in this study are available on request from the corresponding authors.

Footnotes

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

References

Articles from Materials are provided here courtesy of Multidisciplinary Digital Publishing Institute (MDPI)

Similar Articles

To arrive at the top five similar articles we use a word-weighted algorithm to compare words from the Title and Abstract of each citation.

Comparison of trapped charges and hysteresis behavior in hBN encapsulated single MoS2 flake based field effect transistors on SiO2 and hBN substrates.

Nanotechnology, 29(33):335202, 22 May 2018

Cited by: 11 articles | PMID: 29786609

Reduction of Threshold Voltage Hysteresis of MoS2 Transistors with 3-Aminopropyltriethoxysilane Passivation and Its Application for Improved Synaptic Behavior.

ACS Appl Mater Interfaces, 11(23):20949-20955, 30 May 2019

Cited by: 3 articles | PMID: 31117422

Electrically Tunable Room Temperature Hysteresis Crossover in Underlap MoS2 Field-Effect Transistors.

ACS Appl Mater Interfaces, 13(7):9186-9194, 08 Feb 2021

Cited by: 0 articles | PMID: 33555851

Flexible Molybdenum Disulfide (MoS2) Atomic Layers for Wearable Electronics and Optoelectronics.

ACS Appl Mater Interfaces, 11(12):11061-11105, 18 Mar 2019

Cited by: 39 articles | PMID: 30830744

Review

Funding

Funders who supported this work.

Carl Zeiss Foundation (1)

Grant ID: P2018-01-002

European Fund for Regional Development (2)

Grant ID: EFRE-OP 2014–2020

Grant ID: FKZ Raman 2021 FGI 0032